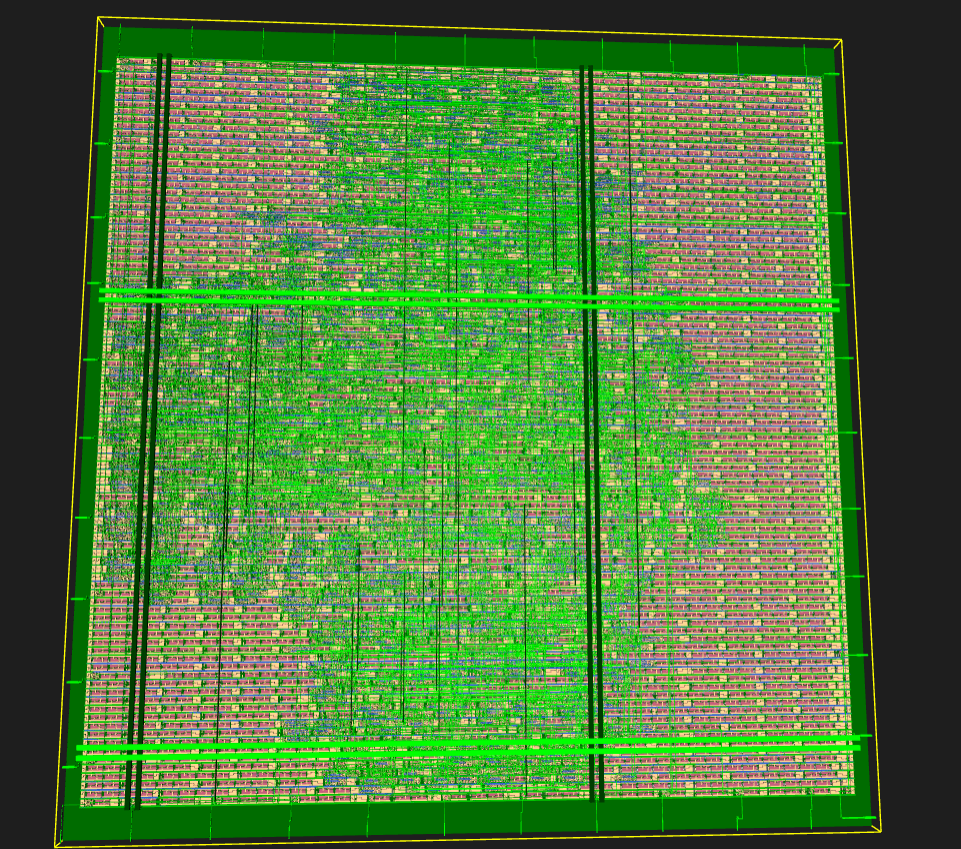

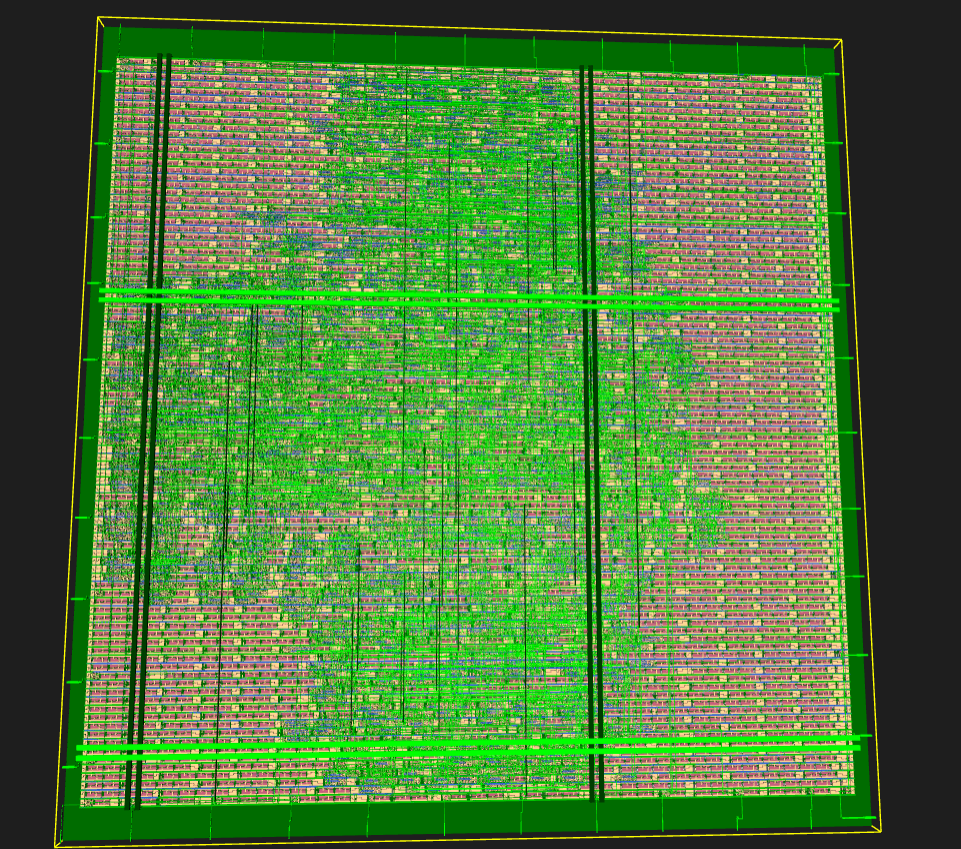

NoC Router RTL2GDSII

Implementation of a 2D-mesh Network-on-Chip router from RTL to GDSII using the OpenROAD flow and open-source PDKs.

Implementation of a 2D-mesh Network-on-Chip router from RTL to GDSII using the OpenROAD flow and open-source PDKs.

Fair round-robin bus arbiter with starvation-free scheduling and multi-testbench verification.

RV32I core with both single-cycle and 5-stage pipelined implementations, including hazard detection and forwarding.

Dual-clock asynchronous FIFO with Gray-coded pointers, synchronizers, and focused CDC verification.

Sensor-driven traffic controller with emergency override, adaptive timing, and waveform-verified state coverage.

Production-ready FIFO with Gray-code pointers, full/empty detection, and clean CDC boundaries for SoC datapaths.

True dual-port memory with configurable depth/width, read-during-write definition, and collision detection.

Structural implementation of an 8×8 Dadda multiplier with delay and power analysis at 45 nm.

Parameterizable LFSR for pseudo-random sequence generation, suitable for DFT pattern generation and simple cryptographic primitives.

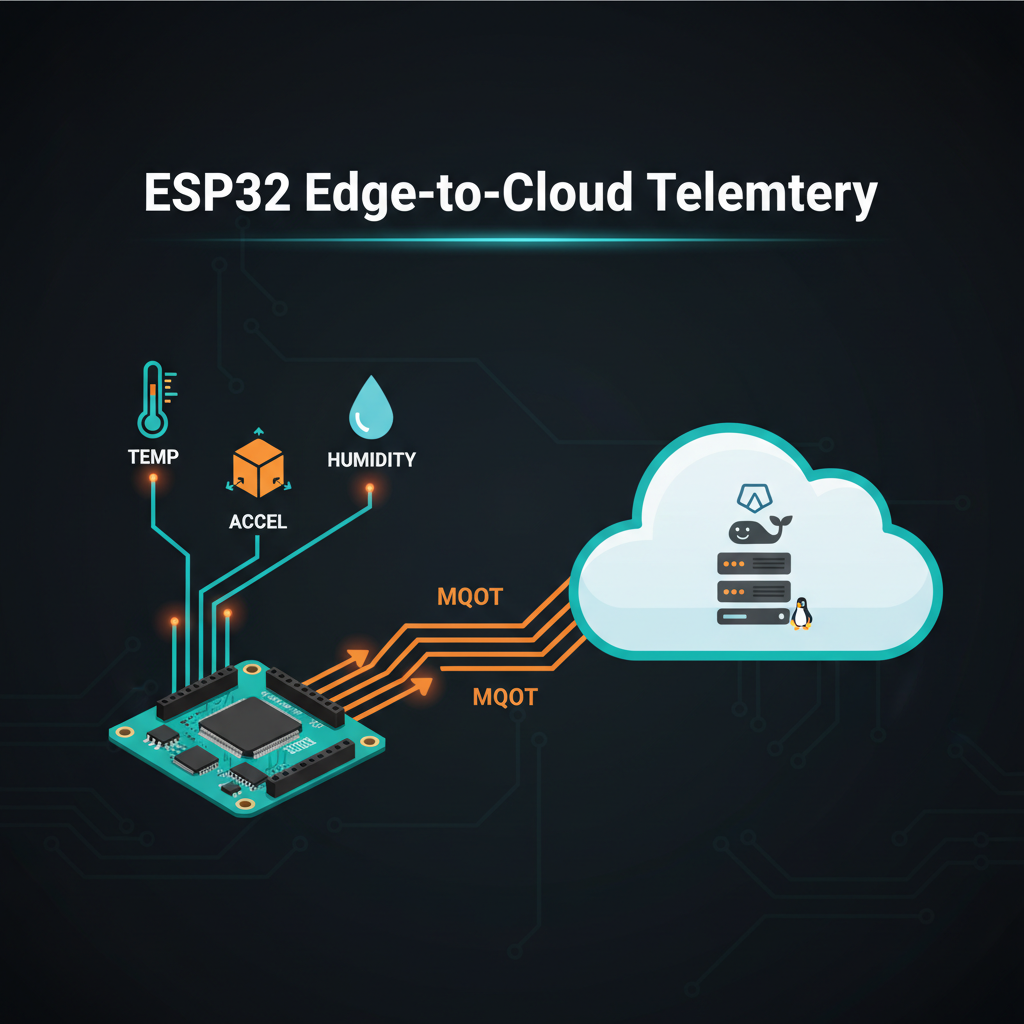

Firmware platform for ESP32-based multi-sensor telemetry with real-time acquisition, local buffering, MQTT-based cloud sync, and robust delivery under intermittent networks.

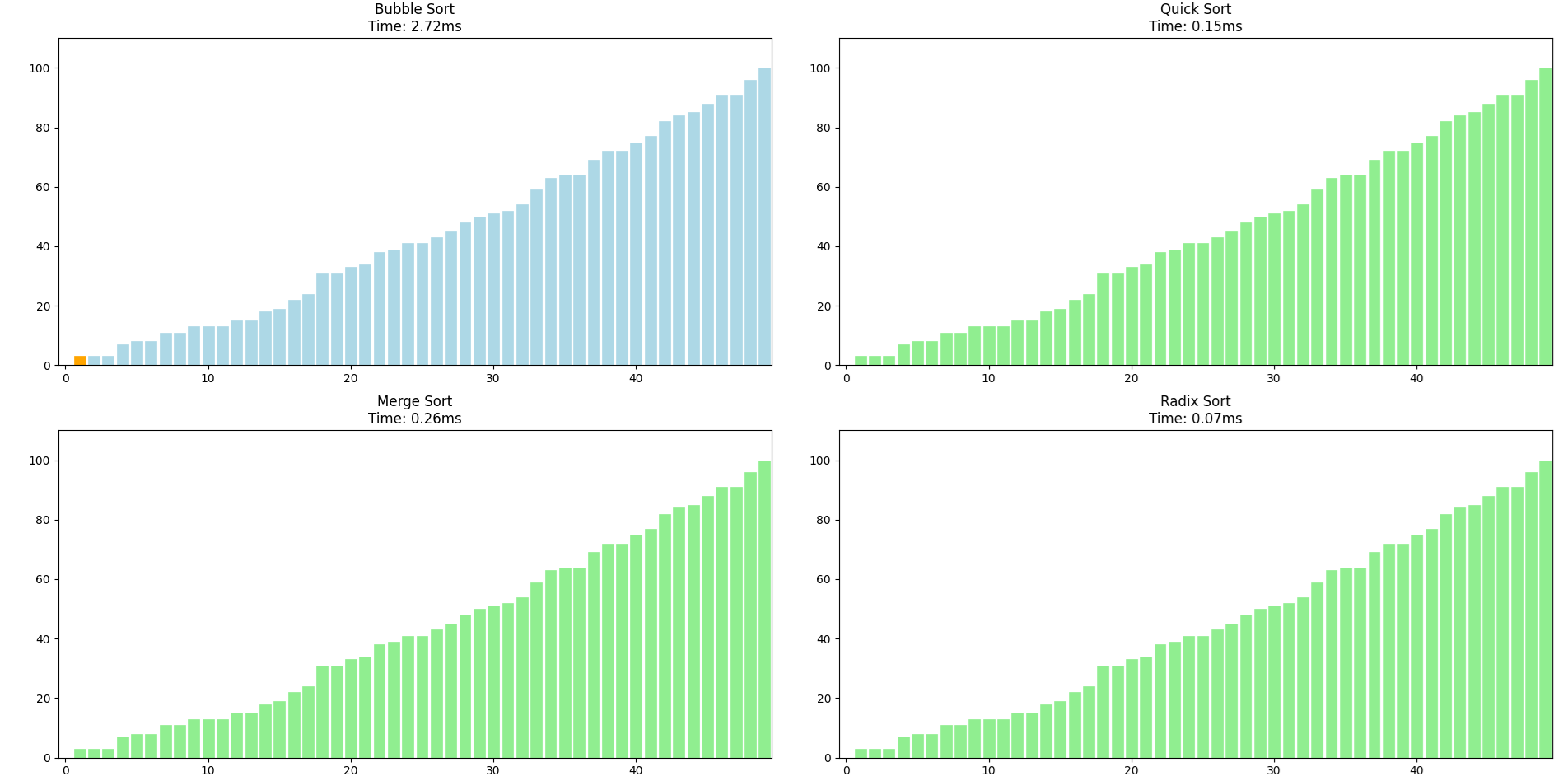

Python-based GUI to visualize classic sorting algorithms and their time-step evolution.

Technical insights on VLSI design, RTL, verification, and hardware engineering.

Understanding why synthesizable RTL doesn't guarantee efficient FPGA implementation covering BRAM inference, resource optimization, and critical timing verification.

A deep dive into Verilog synthesis fundamentals, exploring constructs, blocking vs non-blocking assignments, and why some code translates to hardware while others don't.

Exploring how AI's explosive growth is straining global RAM supply chains and reshaping memory architecture demands.

Demystifying the fundamental differences between Hardware Description Languages and Programming Languages, from syntax to execution models.

Dive deeper into my technical writing on RTL design, verification, FPGA implementation, synthesis, and hardware engineering topics.

View All Posts →WinWinLabs (Volunteer) | Remote | Aug 2025 – Present

Purdue University | Indianapolis, IN | Aug 2024 – May 2025

Thyssenkrupp Crankshaft Company | Illinois, USA | May 2024 – Aug 2024

21 Knots Engineering | Mumbai, IN | Feb 2022 – Jul 2023

Petrocil Engineering | Mumbai, IN | Jun 2019 – Jan 2022

Selected coursework and industry training across computer architecture, RISC-V, Git, RTL design, and Cadence flows.

Open to opportunities in VLSI design, verification, and physical implementation. Let's connect!